October 25<sup>th</sup> - 28<sup>th</sup>, 2016 Campinas, Brazil

11<sup>th</sup> International Workshop on Personal Computers and Particle Accelerator Controls

Dear colleagues,

Welcome to Brazil and to CNPEM!

Thank you all for coming. This year we complete twenty years of the PCaPAC workshop series, and also twenty years of the first electron beam around the accelerator at LNLS (Brazilian Synchrotron Light Laboratory). These days in 2016 are a special time to celebrate!

For the first time, Brazil is the host of a workshop in the accelerators control field. Nevertheless, this country is well acquainted to the matter. The LNLS accelerator complex has produced its first electron beam in 1996. In order to reach this, ten years of preparation under severe conditions were necessary: a decade-long struggle for funding during an era of high inflation rates and of policies that aimed to limit the importation of IT goods. Brazilian young engineers and physicists faced the challenge and reached success. They created a whole system of data acquisition devices, which remain the basis of the LNLS accelerator control system, and which was made available to the local industry, at some extension.

We are here to exchange achievements and experience. But, in addition, we would like to proudly present to you the project and the construction works of SIRIUS, a fourth-generation accelerator, which involves enormous engineering challenges. The LNLS team, with many new-generation young engineers who joined us, will enjoy the opportunity to show and validate some of their ideas around the project.

I would like to thank you all for the contribution to the program, of course, through a talk, a poster or a tutorial session. I leave also my acknowledgment to the invaluable advices from the colleagues in the international Programme Committee. Last but not least, I leave my gratitude to the members of the Local Organisation Committee, from different areas of CNPEM. These months of intense planning and organizing for this PCaPAC workshop brought us even closer.

May we all have a great time!

James Rezende Piton james@Inls.br

PCaPAC 2016 Programme Committee, chair Beamline Software Group, LNLS/CNPEM

LNLS - Brazilian Synchrotron Light Laboratory CNPEM - Brazilian Center for Research on Energy and Materials

#### **ORGANIZERS | SCIENTIFIC COMMITTEE**

- 1. Y.-M. Abiven (SOLEIL)

- 2. A. Arkilic (BNL)

- 3. M. Abbott (DIAMOND)

- 4. R. Bacher (DESY)

- 5. L. Catani (INFN)

- 6. J.-M Chaize (ESRF)

- 7. M. Clausen (DESY)

- 8. M. Clift (AS)

- 9. P. Duval (DESY)

- 10. R. Farnsworth (APS)

- 11. P. Jemian (ANL)

- 12. N. Kamikubota (KEK)

- 13. T. Kosuge (KEK)

- 14. R. Lange (ITER)

- 15. O. Matilla (ALBA)

- 16. W. Mexner (KIT)

- 17. T. Mooney (APS)

- 18. J. Piton (LNLS), chair

- 19. M. Plesko (Cosylab)

- 20. T. Straumann (SLAC)

- 21. D. Tavres (LNLS)

- 22. J. Weber (LBL)

- 23. D. Zimoch (PSI)

#### **LOCAL COMMITTEE**

- 1. Daniel de Oliveira Tavares (LNLS/CNPEM)

- 2. Fábio Reis Fonseca (CNPEM)

- 3. Gustavo Barbosa Monteiro Bruno (LNLS/CNPEM)

- 4. Harry Westfahl Jr. (LNLS/CNPEM)

- 5. Ildéria Maíra dos Santos (CNPEM)

- 6. James Rezende Piton (LNLS/CNPEM)

- 7. Lucas Maziero Russo (LNLS/CNPEM)

- 8. Lucas Sanfelici (LNLS/CNPEM)

- 9. Luciana Noronha (CNPEM)

- 10. Pâmela Machado (CNPEM)

- 11. Renan Picoreti (LNLS/CNPEM)

CONTENTS

#### **Contents**

| Pr | eface                                                                                                                                                                               | i   |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | Foreword                                                                                                                                                                            | iii |

|    | Committees                                                                                                                                                                          | iv  |

|    | Contents                                                                                                                                                                            | V   |

| Pa | pers                                                                                                                                                                                | 1   |

|    | WECSPLIO01 – The Sirius Motion Control Report                                                                                                                                       | 1   |

|    | WECSPLCO02 – Control System Evolution and the Importance of Trial and Error                                                                                                         | 6   |

|    | WECSPLCO03 – Software Tests and Simulations for Control Applications Based on Virtual Time                                                                                          | 10  |

|    | WECSPLCO04 – Development and Current Status of a Carborne Gamma-Ray Survey System, Kurama-II                                                                                        | 13  |

|    | WEUIPLIO01 – Augmented User Interaction                                                                                                                                             | 16  |

|    | WEUIPLCO04 – A Cython Interface to EPICS Channel Access for High-level Python Applications                                                                                          | 21  |

|    | WEPOPRPO03 – Recent Beamline Interlock System and STARS at the Photon Factory                                                                                                       | 25  |

|    | WEPOPRPO10 – Personal Safety System in Sesame                                                                                                                                       | 28  |

|    | WEPOPRPO11 – Recent Improvements to the RIKEN RI Beam Factory Control System                                                                                                        | 31  |

|    | WEPOPRPO12 – Integration of Standalone Control Systems into EPICS-Based System at RIKEN RIBF                                                                                        | 35  |

|    | WEPOPRPO18 – Automated Availability Statistics                                                                                                                                      | 38  |

|    | WEPOPRPO20 - Multipurpose Vacuum Chamber - Automation, Interlock-System and Self-Operating Vacuum                                                                                   |     |

|    | Routines                                                                                                                                                                            | 41  |

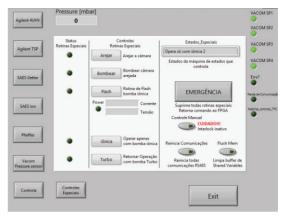

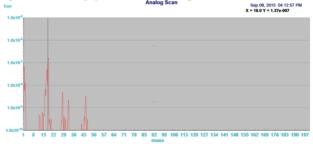

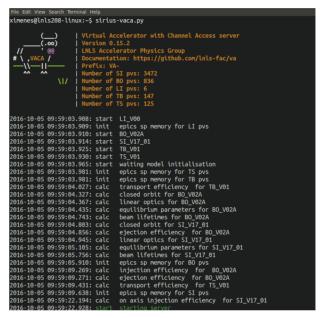

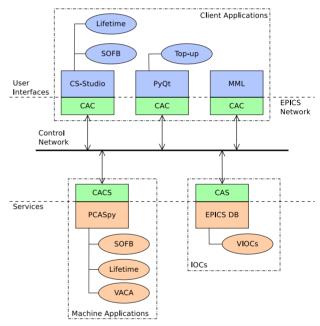

|    | WEPOPRPO21 – Development of a Virtual Accelerator for Sirius                                                                                                                        | 45  |

|    | WEPOPRPO22 – High Level Applications for Sirius                                                                                                                                     | 47  |

|    | WEPOPRPO23 – Beamline Supervisory System Using a Low-Cost Single-Board Computer                                                                                                     | 50  |

|    | WEPOPRPO24 – VDE - Virtual Documentation Environment                                                                                                                                | 53  |

|    | WEPOPRPO25 – Using Tkinter of Python to Create Graphical User Interface (GUI) for Scripts in LNLS                                                                                   | 56  |

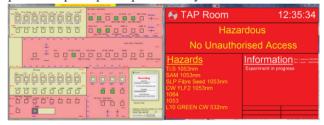

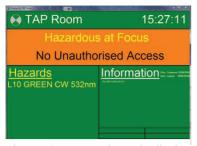

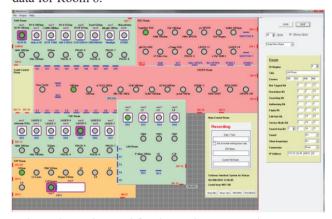

|    | WEPOPRPO26 - Developments of the 'Cerberus' Laser Interlock and Hazard Display System and Associated                                                                                |     |

|    | Design Tool                                                                                                                                                                         | 59  |

|    | THKTPLK01 – Open Hardware and Collaboration                                                                                                                                         | 61  |

|    | THHWPLIO01 – PandABox: A Multipurpose Platform Adapted for Multi-technique Scanning and Feedback                                                                                    | 67  |

|    | THHWPLCO02 – New Controls Platform for SLAC High-Performance Systems                                                                                                                | 72  |

|    | THHWPLCO04 – Open Hardware Experience on LNLS' Beam Diagnostics                                                                                                                     | 75  |

|    | THDAPLCO01 – Embedded Control System for Programmable Multi-Purpose Instruments                                                                                                     | 80  |

|    | THDAPLCO03 – Gateware and Software Frameworks for Sirius BPM Electronics                                                                                                            | 84  |

|    | THDAPLCO06 – A Framework for Development and Test of xTCA Modules With FPGA Based Systems for Particle                                                                              |     |

|    | Detectors                                                                                                                                                                           | 88  |

|    | THPOPRPO03 – UVX Control System: An Approach with Beaglebone Black                                                                                                                  | 91  |

|    | THPOPRPO04 – openMMC: An Open Source Modular Firmware for Board Management                                                                                                          | 94  |

|    | THPOPRPO05 – Implementation of a Precision Logarithmic Ammeter                                                                                                                      | 97  |

|    | THPOPRPO09 – Operation Experience and Migration of I/O Controllers for J-PARC Main Ring                                                                                             | 101 |

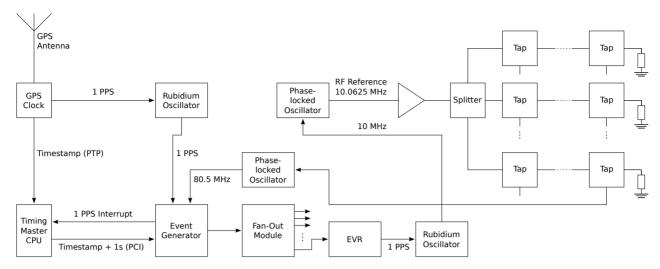

|    | THPOPRPO10 – Timing and Synchronization at FRIB                                                                                                                                     | 105 |

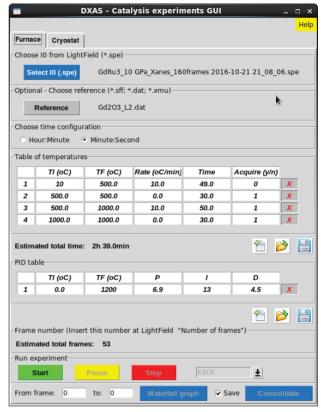

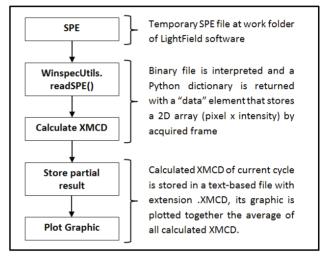

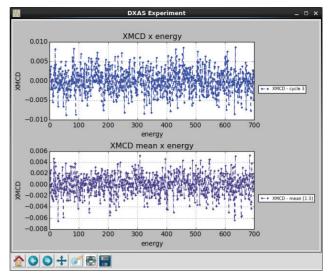

|    | THPOPRPO11 – Processing SPE Files from Princeton Instruments during Data Acquisition in LNLS                                                                                        | 108 |

|    | THPOPRPO13 – High Level Software for the Commissioning of the European XFEL THPOPRPO14 – Automation of the Magnetic Field Measurements of the Air Coils by Means of the Moving Wire | 110 |

|    | ·                                                                                                                                                                                   | 114 |

|    | System                                                                                                                                                                              | 117 |

|    | THPOPRPO22 – Orbitkorrektur, a Java Client for Transverse Orbit Correction in PETRA-III                                                                                             | 120 |

|    | THPOPRPO23 – Fast Orbit Feedback at DELTA                                                                                                                                           | 123 |

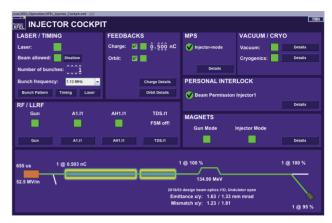

|    | THPOPRPO27 – High-Level Application Development and Production Infrastructure at TRIUMF                                                                                             | 126 |

|    | FRFMPLCO01 – Status of the NSLS-II LLRF System                                                                                                                                      | 129 |

|    | FRFMPLIO03 – Overview of Some Feedback & Control Systems at Synchrotron Soleil                                                                                                      | 132 |

|    | FRFMPLCO05 – A Fast, Custom FPGA-Based Signal Processor and Its Applications to Intra-Train Beam Stabili-                                                                           | 132 |

|    | sation                                                                                                                                                                              | 137 |

|    | FRFMPLCO06 – Harmony: A Generic FPGA Based Solution for Flexible Feedback Systems                                                                                                   | 141 |

|    | FRITPLCO01 – Continuous Integration and Continuous Delivery at FRIB                                                                                                                 | 145 |

|    | FRITPLCO04 – Experience Gained during the Commissioning of the Undulator Control System at the European                                                                             |     |

|    | XFEL                                                                                                                                                                                | 148 |

|    |                                                                                                                                                                                     |     |

Contents

CONTENTS

| Appendices        | 151 |

|-------------------|-----|

| List of Authors   | 151 |

| Institutes List   | 155 |

| Participants List | 159 |

vi Contents

#### THE SIRIUS MOTION CONTROL REPORT

H. D. Almeida, F. P. Figueiredo, M. P. Donadio\*, J. R. Piton LNLS, Campinas, Brazil

#### Abstract

Sirius is the new 4<sup>th</sup> generation synchrotron light source being built in Campinas, Brazil. The motion control report was created to describe all the steps taken to choose the set of motors, motor drives, and controllers that the hardware (GAE) and software (SOL) support groups will recommend. The steps include researching motion control systems in other Synchrotron laboratories, talking to the Sirius beamline designers, defining requirements and testing. This presentation describes the report, showing the information gathering process and latest results.

#### INTRODUCTION

The method to define the motion control solution for Sirius will be based in 7 steps:

- 1. Description of current motion control systems from the UVX synchrotron at LNLS, Brazil, and also from other laboratories, so that it is possible to have a base reference of what can be done and what are the current established practices related to motion control.

- 2. Definition of the requirements for the Sirius motion control system. It focuses on deciding, together with the beamline operators and scientists, what will be necessary for the motion control system to provide (precise movements, coordinated movements, fast movements, etc). It will also include requirements suggested by the support groups, either because they are useful (debugging support, installation on standard racks, etc), or necessary (adherence to safety standards, availability of software drivers, etc). Also, it will be considered the current expertise in equipment used in UVX as a requirement.

- 3. Initial device selection, where the requirements are formalized and the list of possible devices is presented. The result of this step is a filtered and standardized description of everything that beamline operators need from the motion control system and also a list of devices that will be part of the selection process.

- 4. Definition of tests. A set of tests will be elaborated in a way to identify the devices that comply with the requirements or not. The result of this step is a set of programs, types of equipment and textual descriptions necessary to execute the tests.

- 5. Execution of tests. All devices that we can acquire from the pre-selected list will be tested as necessary. The result of this step is a list of devices that passed the tests.

- 6. Reevaluation of tests. This step is basically doing the fourth and fifth steps again, if necessary.

7. Final device selection. The devices will be selected according to tie break rules. The result of this step is the set of recommended motion control devices for Sirius, which complete the report.

#### CURRENT STATE OF MOTION CONTROL SYSTEMS

The UVX light source at LNLS uses motors in the beamlines to control the beam setup, for example, to place mirrors in position, and also to control the experiments, for example, by selecting the energy from the monochromator.

#### Controllers

The main controllers used are the Galil DMC-4183 and Parker OEM 750X, which also has an integrated driver. There are a few IMS (integrated controller and motor) models 14A4, 17C4-EQ and 23C7-EQ and a few All-motion, models: EZHR17EN and EZHR23NHC.

#### Drivers

Basically, there are 3 drivers in use: Galil DMC 4140, Parker OEM750X, and Phytron ZMX+.

#### Motors and Control System Setup

There are many examples of motors used for beamline setup. For example, there are motors for positioning the first mirrors on the beamline entry point. The mirrors position the beam before entering the monochromator. The monochromator base may also contain motors, which will influence both the entry and exit positions of the beam at the monochromator. After the monochromator, motorized slits will select relevant parts of the beam, for example, the most uniform section of the beam, or some part with certain polarization properties. Another motorized set of slits farther away from the monochromator blocks scattered light. The table that holds all the equipment after the monochromator may rotate starting from the monochromator, to guide the light exiting the monochromator at different angles.

All those motors are used to set up the beamline, for example, to focus the beam at a precise point or to select the energy on fixed energy beamlines. They are set up before the experiments start.

Other motors are used during the experiment. Motors may move inside the monochromator to select the energy while doing scans. Sample holders move to select and position different samples to be tested. The samples or the cameras may be rotated to measure diffraction at different angles. The undulator needs to move synchronized with the monochromator to select different energies.

The motor types used at UVX are stepper motors and piezo. The stepper motor brands are Arsape, Haydon Kerk,

ICDN 070 2 05450 100 /

yright © 2017 CC-BY-3.0 and by the respective aut

<sup>\*</sup> marcio.donadio@lnls.br

2

IMS, Kalatec, Lin, Newport, Parker, Phytron, Sanyo Denki, Slo Syn, Syncro, Thorlabs, and Vexta. The piezo motor brands are Newfocus, Newport, and Pi. Some Phytron motors are specially built to operate in the vacuum.

#### Motion Control Software

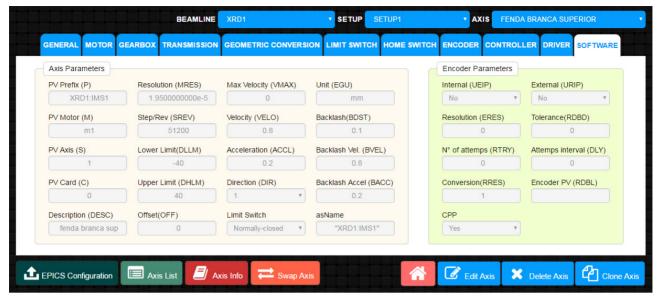

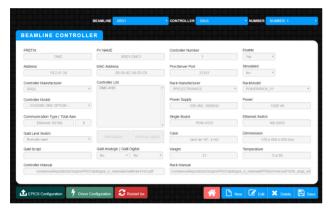

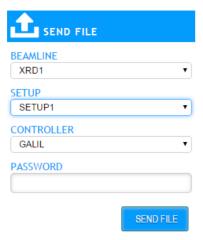

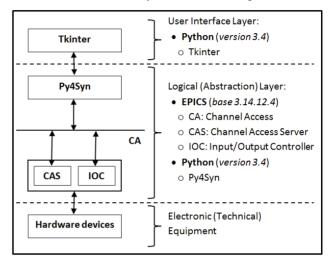

The LNLS control system is almost completely standardized on using the EPICS [1] middleware. EPICS exports remote resources representing devices as remote variables (called "process variables") and organized into records. Motors are exported as motor records [2], with each kind of controller having its own server (called "IOC", or Input/Output Controller). Movement commands or automation is achieved by using scripts sending commands to change and read process variables. For example, a scan script, typically written in python, will connect to the process variables representing slits, change the process variable to move the slit motors to the new position and then measuring beam intensity by reading a process variable representing a photo-diode. This allows doing beam alignment.

Beamline operators may either write their own scripts from zero, or they may use the Py4Syn [3–5] library, developed at LNLS, which contain common procedures, like doing scans, plotting, fitting and storing data files. A set of example front-end scripts, that uses Py4Syn, is also available for beamline operators that don't want to program anything.

# MOTION CONTROL IN OTHER ORGANIZATIONS

Research articles [6–43] explaining or citing parts of the motion control choices in other synchrotron labs were collected. Other particle accelerators with participation in ICALEPCS 2015 were also researched [44–51]. Also, emails were sent to some labs to gather direct information.

#### VME Devices

The following organizations use or have used VME controllers:

- CLS, BESSY, LCLS, PETRA, SSRF and SLS: OMS MAXy controller.

- DELTA and SLS: OMS VME58 controller.

- RHIC: OMS VX2 controller.

- APS and BESSY: Delta Tau PMAC2-VME controller.

- Spring-8: Advanet Advme2005 controller.

The combination of the VME motion controller with other VME devices and VxWorks is used to provide an integrated deterministic control system.

#### In-house Developed Devices

Some organizations have opted to develop devices or parts of devices in-house, the most evident example being the IcePAP system, developed by ALBA and ESRF and expected to be adopted by MAX IV and Solaris. IcePAP is composed of a rack with power supply, the controller, and driver boards. Up to 16 racks can be linked together to control a total of 128

motors. The IcePAP development was motivated by reducing compromises perceived to be present with off-the-shelf controllers. The project goal was to optimize functionality, performance, ease of deployment, a level of standardization and cost.

Another custom device is the YAMS system, developed at Elettra. The system uses a Galil DMC-21x3 controller as the basis of the project. It includes a rack for controller and drivers. The driver boards are custom designed, using the IMS/Schneider Electric IM48xH/IM805H micro stepping drivers. Encoder daughter boards were also designed. The YAMS development was motivated by standardization and costs.

Other in-house custom devices are an RS-485 based motion control system developed at RRCAT using the Texas Instruments LMD18245 driver chip and at Spring-8, a DeviceNet PLC based controller, and the PC-based Blanc4 controller.

#### Host Communication Protocols

There are many protocols and buses available for communication with the host machines or the rest of the control system. Some of them are listed here:

- Newport ESP7000: GPIB, RS-232 and USB

- Delta Tau PMAC2-VME: VME

- OMS MAXnet: Ethernet+TCP/IP and RS-232

- Galil DMC-21x3: Ethernet+TCP/IP, Ethernet+UDP/IP and RS-232

- OMS MAXv: VME

- Newport XPS: Ethernet+TCP/IP

- Parker 6K: Ethernet+TCP/IP and Ethernet+UDP/IP

- Delta Tau Turbo PMAC2: VME

- Delta Tau GeoBrick LV IMS: Ethernet+TCP/IP, USB and RS-232

- Adlink PCI-8134: PCI

- OMS VME58: VME

- Hytec IP8601: VME+IndustryPack

- IcePAP: Ethernet

- National Instruments PCI-STEP-4CX: PCI

- Attocube ANC300: Ethernet+TCP/IP, USB and RS-232

- Aerotech Ensemble CP10: Ethernet, USB and RS-232

- OMS VX2: VME

- Newport MM4006: RS-232, GPIB and RS-485

- Galil DMC-4183: Ethernet+TCP/IP, Ethernet+UDP/IP, USB and RS-232

- Delta Tau Power PMAC: Ethernet

- Tsujicon PM16C: Ethernet+TCP/IP, RS-232 and GPIB

- Advanet Advme2005: VME

- Interface Corporation PCI-7414M: PCI

- Galil DMC-1000: ISA

- Delta Tau PMAC PCI: PCI

- Galil DMC-40x0: Ethernet and RS-232

#### High Precision Devices

While there have been well-described efforts to standardize stepper and servo motor controllers in other labs, no

related efforts seem to have been done for piezo motors. For example, in MOCRAF 2015, it has been described the NSLS-II usage of a Delta Tau and Newport controllers for stepper and servo motors, while the list for piezo motors is composed of SmarAct, Attocube, PI, PiezoJena, and nPoint.

High precision may be used when building instruments, like microscopes or interferometers and on beamlines they are typically used to move sample holders or focusing and correcting small-scale positioning errors. A more specific use case exists at BESSY, a Nanomotion HR8 piezo motor is used to rotate the monochromator grating and mirror. Outside beamlines, the European XFEL has described at ICALEPCS 2015 the piezo-based cavity fine tuner, which reduces deformation on the accelerator's walls.

#### Complex and Coordinated Motion

Motions that happen on an arbitrary nonlinear path over time will be considered complex motions in this paper. Coordinated motion is a motion that simultaneously moves more than one motor.

Examples in complex motions: to change the monochromator energy in fixed energy steps, nonlinear movement with variable speed is required by the monochromator motors between each step. If a slit can move independently its top, bottom, right and left blades, then the operation of increasing the gap in the slit is a linear coordinated movement.

A nonlinear movement may also happen at a lower level, like in piezo devices, which may be nonlinear in nature. With the help of position encoders and closed loop feedback they might be translated and interpreted at higher levels as linear movements, if necessary.

An example of complex motion at SOLEIL comes from the ICALEPCS 2015 report on the REVOLUTION project. A beamline had its motion controller switched to a Delta Tau Power Brick to control the beamline energy selection. Seven equations were implemented to translate the required energy to the positions of each of the seven motors inside the monochromator so that only the high-level request for a specific energy is required. The goals of the implementation were to reduce communication with the host machine and to allow continuous energy scan operations.

At BESSY, a Nanomotion HR8 piezo motor uses a Delta Tau PMAC2-VME controller with a custom nonlinear model and closed loop feedback to overcome the encoder precision limitations when moving the piezo motor in very small steps. The motion also needs to be synchronized with the undulator for correct energy selection.

Another example of complex and coordinated motion is the SLAC LCLS fast wire scanner, used for beamline emittance diagnostics, which uses the S-curve available in the OMS/ProDex MAXv controller.

#### REQUIREMENTS FOR THE SIRIUS MOTION CONTROL SYSTEM

#### UVX as the Baseline

The beamline requirements for Sirius might not be well defined. For example, the beamline operators and scientists may not know what they need. The current motion control environment in UVX may be used as a baseline for these cases. Knowledge and expertise on the current solution are also considered requirements with strong importance. This is because it took years of work from LNLS workers to understand, correct and develop hardware and software until the system stabilized. Probably this work needs to be redone when choosing different components.

#### Standardization of Components

We expect to follow an 80% / 20% rule, considering a cheap and simple solution for 80% of the motors and an expensive, precise and resource-full solution for the remaining 20%, regarding complex and coordinated motion. In particular, we expect that a single selection of components will be useful for the majority of use cases. For the more specific cases either one or more sets of components will be required, the less, the better for administration and maintenance costs.

#### Requirements for the New Beamlines

Currently, out of the 13 initial beamlines planned for Sirius, 5 of them have an approved preliminary design report. We have talked to the beamline scientists about the motion control system of these 5 lines and also with 1 other scientist for the remaining beamlines. The discussed requirements are detailed below.

**Sapucaia** The Sapucaia beamline will be an SAXS beamline, with support for doing "nanobeam" experiments.

The main beamline elements are:

- the initial slits after the protection wall

- a double crystal monochromator

- a positioning mirror

- two sets of slits for slicing and focusing the beam

- kinoform lenses to focus the nanobeam

- the sample holder stage

- the X-ray detectors, that detect light scattered from the samples.

Cateretê The Cateretê beamline is defined as a coherent and time-resolved X-ray scattering beamline. It will support time-resolved small angle X-ray scattering (SAXS) and ultra-small-angle X-ray scattering (USAXS), which are techniques for structural studies of nanoparticles, coherent diffractive imaging (CDI), a technique for 3D imaging with 30 nm resolution that uses coherent X-ray scattering instead of lenses and X-ray photon correlation spectroscopy (XPCS), for studying dynamics of nanoparticles using fluctuating patterns generated by coherent X-ray scattering.

The main beamline elements are:

the undulator at the storage ring

ight © 2017 CC-BY-3.0 and by the respective a

- the initial slits

- · a double crystal monochromator

- · a focusing mirror

- a set of slits for slicing the beam

- the sample stage

- · the detector stage

**Carnaúba** The Carnaúba beamline is defined as a nano focus beamline, providing a beam focused to a diameter of up to 80 nm. It targets fluorescent and absorption techniques, as well as imaging based on X-ray scattering.

The main beamline elements are:

- · the undulator at the storage ring

- · the initial slits

- a focusing mirror

- a second mirror for positioning and removing harmonics

- a set of slits used as the secondary light source

- a 4-bounce crystal monochromator

- a set of slits after the monochromator to slice the beam

- a Kirkpatrick-Baez mirror for focusing the beam at nanometric scale

- the sample holder station

**Ipê** The Ipê beamline targets soft X-ray spectroscopy, with an energy range of 100 eV to 2.000 eV and will have two separate experimental end stations for two different techniques: resonant inelastic X-ray scattering (RIXS), which uses emitted photons, and near ambient pressure X-ray photoelectron spectroscopy (NAP-XPS), which uses emitted electrons to perform the spectroscopic measurement. The main beamline elements are:

- the undulator at the storage ring

- · a first mirror used as a filter to reduce thermal load

- a grating and mirror (planar grating) monochromator

- a deflecting mirror used to switch between the two end stations

- a set of slits after the monochromator to slice the beam before each end station

- · focusing mirrors for each end station

- sample stages on each end station

- · detector stages on each end station

#### RESULTS AND DISCUSSION

Step 2 of the motor selection procedure was concluded and the requirements were partially described in this paper. Next step, the initial device selection will start.

#### **CONCLUSION**

An extensive work needs to be done to finish this procedure. When we have the final results a new report will be written.

#### **REFERENCES**

[1] EPICS, http://www.aps.anl.gov/epics

- [2] EPICS: Motor Record and Device/Driver support, http://www.aps.anl.gov/bcda/synApps/motor

- [3] Py4Syn GitHub, https://github.com/hhslepicka/ py4syn

- [4] Py4Syn Documentation, http://py4syn.lnls.br

- [5] H. H. Slepicka et al., "Py4Syn: Python for Synchrotrons", J. Synchrotron Rad., vol. 22, pp. 1182-1189, 2015.

- [6] D. Hernández-Cruz, A. P. Hitchcock, T. Tyliszczak, M.-E. Rousseau, and M. Pézolet, "In situ azimuthal rotation device for linear dichroism measurements in scanning transmission x-ray microscopy", Rev. Sci. Instrum., vol. 78, p. 033703, 2007.

- [7] E. Gann et al., "Soft x-ray scattering facility at the Advanced Light Source with real-time data processing and analysis", Rev. Sci. Instrum., vol. 83, p. 045110, 2012.

- [8] D. J. Vine *et al.*, "An in-vacuum x-ray diffraction microscope for use in the 0.7-2.9 keV range", *Rev. Sci. Instrum.*, vol. 83, p. 033703, 2012.

- [9] S. Stepanov *et al.*, "JBluIce-EPICS control system for macromolecular crystallography". *Acta Crystallogr. D Biol. Crystallogr.*, vol. 67, pp. 176-188, 2011.

- [10] D. Zangrando et al., in Proc. EPAC'08, pp. 2329-2331.

- [11] N. Janvier, J. Clement, P. Fajardo, and G. Cuní, in *Proc. ICALEPCS'13*, pp. 766–769.

- [12] K. Cerff, D. Haas, D. Jakel, and M. Schmitt, in *Proc. PCa-PAC'14*, pp. 198-200.

- [13] M. Clift, R. Farnsworth, A. Starritt, and L. Corvetti, "Motion control using EPICS and Galil controllers", presented at ICALEPCS'09, Kobe, Japan, Oct. 2009, paper WEP056, unpublished.

- [14] D. G. Hawthorn *et al.*, "An in-vacuum diffractometer for resonant elastic soft x-ray scattering", *Rev. Sci. Instrum.*, vol. 82, p. 073104, 2011.

- [15] R. Louis *et al.*, "Synchrotron powder x-ray diffractometer beamline at J. Bennett Johnston, Sr., Center for Advanced Microstructures and Devices", *Nucl. Instr. Meth. Phys. Res. Sect A*, vol. 582, pp. 84–86, 2007.

- [16] M. D. Miller, G. N. Phillips, Jr., M. A. White, R. O. Fox, and B. C. Craft, III, "The development of the GCPCC protein crystallography beamline at CAMD", Application of Accelerators in Research and Industry - Sixteenth Int'l Conf., pp.734-740, 2001

- [17] C. Conolly, "Facility upgrades, networking and computing", CHESS News Magazine, pp. 13-16, 2009.

- [18] B. Nutter, in MOCRAF'13, http://www.synchrotron-soleil.fr/images/File/Informatique/Workshop-Motion/Talks/TT01\_Diamond-Nutter-technical-Mocraff-2013.pdf

- [19] U. Berges and S. Döring, in *Proc. ICALEPCS'07*, pp. 232-234.

- [20] M. Lonza et al., in Proc. ICALEPCS'11, pp. 589-592.

- [21] A. Balzer et al., in Proc. ICALEPCS'05, paper MO4B.2-2O.

- [22] K. Horiba *et al.*, "A high-resolution synchrotron-radiation angle-resolved photoemission spectrometer with *in situ* oxide thin film growth capability", *Rev. Sci. Instrum.*, vol. 74, pp. 3406-3412, 2003.

- [23] Y. Nagatani and T. Kosuge, in Proc. PCaPAC'14, pp. 78-80.

- [24] N. Inami, Y. Takeichi, and K. Ono, "Real-time motion control and data acquisition system for scanning x-ray microscopy using programmable hardware", *J. Phys.: Conf. Ser.*, vol. 502, p. 012011, 2014.

- [25] T. Kracht, in MOCRAF'11, http://www.

synchrotron-soleil.fr/images/File/

soleil/ToutesActualites/Workshops/

2011/MotionControl/WS-MoCRaf-Tl.04MotionControlSoleilMay2011.pdf

- [26] M. R. Jathar, in Proc. ICECT'11, vol. 2, pp. 104-106.

- [27] D. M. Gassner et al., in Proc. IPAC'11, pp. 462-464.

- [28] K. Takemoto *et al.*, "Development of an auto-focusing imaging system in the soft x-ray microscope beamline of the SR center in Ritsumeikan University", *J. Phys.: Conf. Ser.*, vol. 186, p. 012019, 2009.

- [29] Z. H. Zhang, W. H. Jia, P. Liu, and L. F. Zheng, in *Proc. IPAC'13*, pp. 2998-3000.

- [30] X. Lan et al., "SPEC application for achieving inelastic xray scattering experiment in the SSRF", arXiv:1508.06726, 2015.

- [31] P. Liu, in *EPICS Collaboration Meeting'11*, http://www.aps.anl.gov/epics/meetings/2011-06/sys/data/16/LIU\_Ping\_BL\_Control.ppt

- [32] Q.-S. Wang *et al.*, "The macromolecular crystallography beamline of SSRF", *Nuclear Science and Techniques*, vol. 26, p. 010102, 2015.

- [33] W. Klysubun *et al.*, "X-ray absorption spectroscopy beamline at the Siam Photon Laboratory", *AIP Conf. Proc.*, vol. 879, pp. 860–863, 2007.

- [34] D. Corruble et al., in Proc. ICALEPCS'13, pp. 81-84.

- [35] S. Z. Zhang et al., in Proc. ICALEPCS'15, pp. 201-204.

- [36] M. Ishii and T. Ohata, in Proc. ICALEPCS'09, pp. 465-467.

- [37] T. M. McPhillips *et al.*, "Blu-ice and the distributed control system: software for data acquisition and instrument control at macromolecular crystallography beamlines", *J. Synchrotron Radiat.*, vol. 9, pp. 401-406, 2002.

- [38] C. L. Li, A. M. Kiss, and W. J. Zhang, in *Proc. IPAC'15*, pp. 1243-1245.

- [39] J. Krempaský et al.., in Proc. ICALEPCS'13, pp. 729-732.

- [40] V. N. Strocov et al., "High-resolution soft X-ray beamline ADRESS at the Swiss Light Source for resonant inelastic X-ray scattering and angle-resolved photoelectron spectroscopies", J. Synchrotron Radiat., vol. 17, pp. 631-643, 2010.

- [41] J. Raabe *et al.*, "PolLux: a new facility for soft x-ray spectromicroscopy at the Swiss Light Source", *Rev. Sci. Instrum.*, vol. 79, p. 113704, 2008.

- [42] I. Saleh and A. Ismail. ftp://ftp.sesame.org.jo/ SESAME-Uploads/SAC-TAC/SAC-TAC-2013/SAC2013/ SAC-2013-Motion\_Control.pptx

- [43] K. Cole, R. R. Vallance, and T. Lucatorto, in *Proc. Precision Mechanical Design and Mechatronics for Sub-50nm Semiconductor Equipment'08*, pp. 117–122.

- [44] R. Walton et al., in Proc. ICALEPCS'15, pp.1-4.

- [45] E. Suljoti, in MOCRAF'15, http://www.synchrotron-soleil.fr/images/File/Informatique/ Workshop-Motion/MOCRAF-2015/MOCRAF2015-AfternoonSession2-03-StatusAndNew DvpInMotionControlAtBESSY-II.pdf

- [46] J. M. D'Ewart, M. Campell, P. Krejcik, H. Loos, and K. Luchini, in *Proc. ICALEPCS'15*, pp. 114-116.

- [47] M. Linberg et al., in Proc. ICALEPCS'15, pp. 240-243.

- [48] P. Goryl et al., in Proc. ICALEPCS'15, pp. 510-512.

- [49] R. A. Kadyrov, J. H. De Long, K. Ha, S. So, and E. Stavitski, in *Proc. ICALEPCS'15*, pp. 881-884.

- [50] W. Lewis, in MOCRAF'15, http://www.synchrotron-soleil.fr/images/File/Informatique/ Workshop-Motion/MOCRAF-2015/MOCRAF2015-MorningSession2-02-NSLS-II.pdf

- [51] C.Y. Liao et al., in Proc. ICALEPCS'15, pp. 1173-1176.

# CONTROL SYSTEM EVOLUTION AND THE IMPORTANCE OF TRIAL AND ERROR

P. Duval, M. Lomperski, DESY, Hamburg, Germany J. Bobnar, Cosylab, Ljubljana, Slovenia

#### Abstract

In this paper we address the importance and benefits of trial and error in control system evolution. Here we refer to the control systems of particle accelerators and large machines, whose control systems, although complex, will not lead to catastrophe in case of failure. We likewise focus on the evolution of control system software, although the issues under discussion will apply to and are often driven by control system hardware. We shall contrast classical Darwinian evolution via natural selection with control system evolution, which proceeds rather via artificial selection, although there are numerous software memes which tend to replicate according to their 'fitness'. The importance of general trial and error, i.e. making mistakes and learning from them, in advancing the capabilities of a control system will be explored, particularly as concerns decision making and overcoming Einstellung.

#### INTRODUCTION

A mature accelerator control system will be able to address a wide variety of problems which might arise throughout the controlled facility's natural lifecycle. Solving new problems or a push to provide better solutions to old problems will generally lead to control system evolution, even if this amounts to little more than keeping up with industrial or commercial components. The way one goes about problem solving will in turn have a marked influence on the pace of this evolution. We will discuss many of these aspects below, finishing with a few concrete examples of control system evolution at play.

#### GOALS AND PROBLEM SOLVING

#### The God Complex and Einstellung

When we are well-versed in our control system and at the same time faced with a new problem or challenge we are apt to fall prey to the God Complex, i.e. that "no matter how complicated the problem, you believe that your solution is correct." [1, 2] This is furthermore often compounded by what psychologists refer to as the *Einstellung* effect, or the "predisposition to solve a given problem in a specific manner even though better or more appropriate methods of solving the problem exist". [3,4]

The danger is not that our problem won't get solved. It most likely will. The danger is that we might not only miss an opportunity to explore new ideas, we might also end up wasting resources, and/or missing the big picture entirely due to our rush to implement a known solution.

#### Priming and Anchoring

Indeed our choices in problem solving and decision making are often due to an implicit memory effect known as priming [5], where exposure or familiarity with one stimulus (or solution paradigm) can influence our response to another. The classic trivial example: "How many animals did Moses take on the ark?" (answer: 0) might appear to have little to do with our decision making until we realize that our expectations can be easily primed, a case of priming known as anchoring [5]. For example, imposing an artificial deadline of one week to try some solution automatically suggests a level of difficulty. Worse, refusing to consider a new solution because "everyone else does it differently" suggests a knowledgeable rejection of the new solution. Unfounded expressions such as "one week" or "everyone else" often serve only to anchor our expectations at some level.

#### Accumulated Advantage

The previous example of anchoring ("everyone else does it differently") is also an example of the effect of accumulated advantage, often referred to as the *Matthew Effect*, (from Matthew 25:29 in the King James version of the Bible) [6]. In point of fact, our opinions are strongly related to and often dependent on those of others. The crowded restaurant *must* serve better food than the empty one next door! In an experiment by Duncan Watts [6], two sets of college students could download garage band music from two web sites. The sites were identical except that in one case the students could see the *likes* and downloads of everyone else. It's not surprising that in one case there were a handful of hit songs and in the other the *likes* and downloads showed a flat distribution.

#### Trial and Error

We should in any case be aware of the aforementioned challenges to our problem solving abilities. Whether we admit that we already know the solution to a new problem or not, the practice of trial-and-error cannot be avoided. The basic algorithm of trial-and-error can be described as:

- 1) Define what constitutes a solution to our problem.

- 2) Try something.

- 3) Check to see if the problem is solved. If not:

- 4) Modify *something* into a more promising direction and repeat step 3). Or, if the problem is solved:

- 5) Ouit.

ISBN 978-3-95450-189-2

6 Control Systems

The psychological effects we have just discussed will of course influence the *something* that we initially try in step 2). In fact, if there is any kind of time pressure the best bet is indeed to go with our best over-all hunch. If on the other hand there is a time-window for bold experimentation, trying several *somethings* might lead to remarkable improvements.

#### **EVOLUTION**

Evolution, Darwinian or otherwise, naturally progresses via trial-and-error. The incremental evolutionary steps might occur by chance, as in the case of the natural world, or by design as in the case of control system evolution. Either way, the measure of success is the ability to replicate. Thus there is an implicit drive to improve.

#### Darwinian Evolution

In Darwinian evolution [7] the replicating unit is the gene. Any mutation which leads to a greater chance of survival will in turn lead to an organism's genetic material replicating itself more often, which is what we mean by improvement. Evolution by natural selection is of course slow and has a direction. That this occurs by chance means that evolutionary changes cannot be reengineered in order to improve performance. Any improvement comes entirely by trial-and-error.

An oft cited *proof* of *intelligent design* by creationists is the eye, which is so complex that it couldn't possibly have happened by chance and *must* have had a designer. A billion years, though, is ample time for cells initially able to only distinguish dark from light to successively evolve into such a remarkable organ. More to the point, the design is actually rather clumsy, as recognized already in the 19<sup>th</sup> century by Hermann von Helmholtz. No engineer would route the wiring leading from a camera's photo cells back into the path of the light source and then bundle it all into a thick cable near the center of the collecting surface, thereby creating a blind spot!

There is no chance to reengineer this into a more sensible solution. Nor is there any chance that a random mutation will fix the design flaws.

It is nonetheless instructive to recognize how incredibly well the eye does work (in tandem with our visual cortex). The design flaws are practically irrelevant, a point which should be remembered when the temptation to refactor complicated, yet well-working, software arises.

#### Software Evolution

Software evolution is driven by design decisions from the very beginning. Although survival might still be of the fittest, the agent of change is artificial- rather than natural-selection, and the replicating unit will be the *meme*, the smallest idea that gets transferred within a culture [8] (e.g. the idea of *sockets* or *threads*, but not necessarily the implementation of them).

Manny Lehman identified three categories of software, S- (*specific*) programs, P- (*procedural*) programs, and E- (*evolutionary*) programs [9]. S-programs are written once for a specific purpose. P-programs implement a set of

procedures only (e.g. play chess). E-programs perform some real-world activity and adapt to the environment and circumstances in which they run.

As much as we might wish particle accelerator control systems to be P-programs, they are in fact E-programs and necessarily evolve. In fact, as the environment in which a control system operates does indeed evolve, one of Lehman's Laws [9] asserts that the quality of the control system will decline unless it also evolves.

Here, however, we do have and often utilize the ability to refactor *bad* or *clumsy* design decisions. Of course, the question remains as to what a bad design is and (like the eye) as to whether it is in the end worth the risk of changing a (well-running and complex) running system merely for the sake of improving the design.

Complex software might also contain vestige routines (analogous to the appendix) which have no practical purpose but continue to be accessed by vintage application programs and are therefore required to exist. Thus, API breaks in reusable software such as control system libraries should be avoided when possible, including the disposal of deprecated API routines or class methods, unless the consequences of doing so are understood beforehand.

In addition to keeping pace with an evolving hardware environment, control system software will evolve on its own accord in order to improve or introduce functionality. The pace of evolution here will be strongly dependent on the developer's susceptibility to the psychological effects mentioned in the previous section.

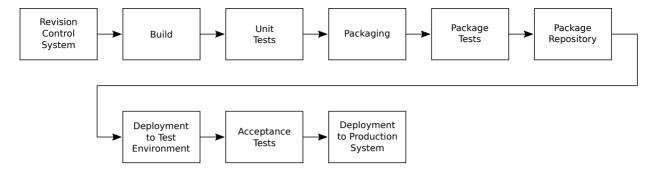

Regardless of pace, any real evolutionary change will occur via trial-and-error. Typically, coding modifications will be run through various unit tests (a tight trial-and-error loop) until there is a new release candidate. The next trial might occur in the field when the software is deployed. After deployment, however, the cost of error will be much higher. In the case of accelerator control there is fortunately little or no chance of catastrophic error (as there is in airplanes or nuclear power). Nonetheless an error can lead to downtime or damage to equipment. Thus the cost of error should be examined along with rollback strategies prior to any new deployment.

#### **EXAMPLES**

#### Control System Protocol

One of the problems we sometimes have to deal with is an unacceptably high load (CPU and/or network) on a control system server. If this load is primarily due to information transfer from server to client then we have an issue with the control system protocol.

The TINE [10] control system makes use of the device server paradigm, where a server exposes control system elements as instances of *devices* and offers access to their attributes and actions through *properties*. It also offers *publish-subscribe* data acquisition, which in itself goes a long way in reducing unnecessary load on a server due to data transfer to multiple clients. However if client applications obtain data via repetitive non-persistent

pyright © 2017 CC-BY-3.0 and by the respective author

transactions (*polling*) then there is no load reduction from *publish-subscribe*. The situation can be compounded many-fold if a server with many device instances (e.g. a vacuum pump, beam position monitor, or power supply controller - PSC) is requested to deliver information from all elements one-at-a-time. And precisely this is an all too common occurrence with simple client panel applications.

When faced with this situation in 2009 with multiple *ddd* [11] clients accessing the FLASH PSCs we decided to eschew the traditional split-the-load-among-multiple-servers approach and add a new feature to the control system protocol called contract coercion [12].

As the PSC server is not only prepared to, but prefers to send property information for all PSC instances for a given property as a multi-channel array, we addressed the question "Can we coerce a client's synchronous request for the value of a property into a monitor for all values of that property?" We answered yes and then introduced contract coercion. The initial results were more than encouraging as the load on the server was effectively decimated without modifying a single line of client code.

To be sure, there was a significant amount of tight-loop trial-and-error with unit tests, etc. prior to deployment, but we were nevertheless aware of the costs of unforeseen errors beforehand. We assumed, based on prior testing, that the likelihood of a serious error on *most* clients was extremely small. If an exotic client did have an error we based the decision to rollback or not on how critical to operations the exotic client was and whether the error appeared immediately or some significant time later.

In the end, no rollbacks were ever necessary. Several errors were nonetheless encountered and repaired in the months following initial deployment. Likewise, the ensuing years saw several quality-of-service additions to the initial contract coercion implementation, each with its own trial-and-error process.

#### Control System Services

The TINE control system offers many central services, among them a plug-and-play system concerning name resolution.

The TINE Equipment Name Server (ENS) maintains a device server database and provides address information when a client needs to contact a control system element. The ENS database can of course be modified by an administrator, but in general it is updated automatically. The plug-and-play mechanism will add a new server to the database or update a server's meta-information with every server start.

This level of automation requires a good deal of trialand-error whenever new features are added. The ENS must not only guarantee a unique entry for a control system server it must also inform any server trying to usurp an existing name that its request was denied. The requested names and meta- information of any new server must also be validated, etc.

When we make modifications here, however we are modifying a central service rather than the control system protocol itself. What are the costs of error in this case?

The ENS would appear to offer a critical service, in contrast to, say, central archive or alarm servers. In fact it is *semi*-critical. All clients already have a fallback mechanism (using the last locally cached address in the event of address resolution failure) when the ENS is not operational. The worst that can happen is either 1) a new server will not be able to plug itself into the system, or 2) an existing server starting on a new host will not be able to modify its address information.

The other TINE central services are even less critical in that operations are never threatened in the event of error.

#### **Applications**

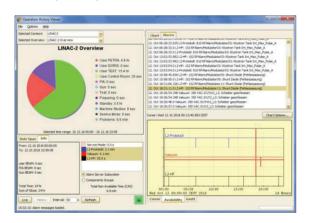

A good example of a specific application with on-going trial-and-error is the Operation History Viewer in TINE Studio [13, 14]. This application shows the machine state information (including problems) over any selected time range. The *problems* state indicates non-availability of the machine and can be divided into sub-systems, where one has the ability to browse through the fatal alarms responsible for the downtime. The goal is to have a fully automatic calculation of operation and availability history. As blame for non-availability is assigned to fatal alarms, we see that the application consists of more than a mere presentation of data, and involves, among other services, the central alarm system in a vital way. We may not break free from the trial-and-error loop here for some time to come and have added the ability to post-correct both the state information and the availability information (by a machine coordinator) over any time interval.

The costs of error here, as for most applications, apply almost exclusively to the application itself, and will have no impact on operations unless the application is critical to operations (which this isn't). This is not to say that we can make errors with impunity. Once an application is regularly used, any degradation in quality of service will of course result in unhappy customers. Ensuring that the most-used features continue to work properly is generally sufficient to allow deployment of a new version. Should an error be discovered, a rollback can easily be made while the error is dealt with.

#### **CONCLUSIONS**

Control system evolution will occur if for no other reason than the necessity of keeping pace with the commercial and industrial world. Real innovation in control system software will involve a trial-and-error period. This period can be extensive or even continual, but primarily constitutes what is meant by control system evolution. Dramatic improvement most often occurs if we resist the psychological pressures to solve any new problems in a tried-and-true manner and admit that we perhaps don't already know the best course of action. Often enough, deadlines will require us to play it safe, but if we have a large enough time window for development such that we can test several solutions to the same problem then we can often make great strides in the advancement of our control systems.

#### REFERENCES

- [1] A. Cochrane, https://en.wikipedia.org/wiki/Archie\_Cochrane

- [2] T. Harford, "Trial, Error and the God Complex"; https://www.ted.com/.

- [3] A. Luchins, "Mechanization in problem solving: The effect of Einstellung". Psychological Monographs, 1942.

- [4] M. Bilali and P. McLeod, "Why Your First Idea Can Blind You to a Better One", Scientific American, March 2014.

- [5] D. Kahneman, "Thinking Fast and Slow", Penguin Books, 2011.

- [6] S. Pinker, "The Better Angels of Our Nature", Viking Press, 2011.

- [7] R. Dawkins, "The Blind Watchmaker" (and references therein), W.W. Norton & Co., 1986.

- [8] R. Dawkins, "The Selfish Gene", Oxford Press, 1976.

- [9] M. Lehman, https://en.wikipedia.org/wiki/Software\_evolution

- [10] TINE, http://tine.desy.de

- [11] iddd, http://jddd.desy.de

- [12] P. Duval and S. Herb, "The TINE Control System Protocol: How to Achieve High Scalability and Performance", in Proc. PCaPAC'10, paper WECOAA02.

- [13] P. Duval, M. Lomperski, and J. Bobnar, "TINE Studio, Making Life Easy for Administrators, Operators and Developers", in *Proc. ICALEPCS'15*, paper WEPGF133.

- [14] P. Duval, M. Lomperski, H. Ehrlichmann, and J. Bobnar, "Automated Availability Statistics", presented at PCaPAC'16, Campinas Brazil, Oct. 2016, paper WEPOPRPO18, this conference.

# wight @ 2017 CC\_RV-3 0 and by the reenective outhors

10

# SOFTWARE TESTS AND SIMULATIONS FOR CONTROL APPLICATIONS BASED ON VIRTUAL TIME

M. Hierholzer\*, M. Killenberg, T. Kozak, N. Shehzad, G. Varghese, M. Viti, DESY, Hamburg, Germany

#### Abstract

Ensuring software quality is important, especially for control system applications. Writing tests for such applications requires replacing the real hardware with a virtual implementation in software. Also the rest of the control system which interacts with the application must be replaced with a mock. In addition, time must be controlled precisely. We present the VirtualLab framework as part of the Chimera Tool Kit (formerly named MTCA4U). It has been designed to help implementing such tests by introducing the concept of virtual time, and combining it with an implementation basis for virtual devices and plant models. The virtual devices are transparently plugged into the application in place of real devices. Also tools are provided to simplify the simulated interaction with other parts of the control system. The framework is designed modularly so that virtual devices and model components can be reused to test different parts of the control system software. It interacts seamlessly with the other libraries of the Chimera Tool Kit such as DeviceAccess and the control system adapter.

#### INTRODUCTION

To test software automatically, a virtual test environment has to be provided. With the VirtualLab framework the necessary tools for this tasks are available. The framework is part of the Chimera Tool Kit and is available as open-source software [1].

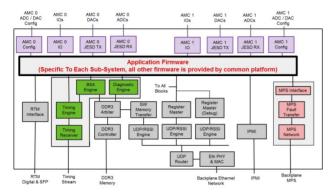

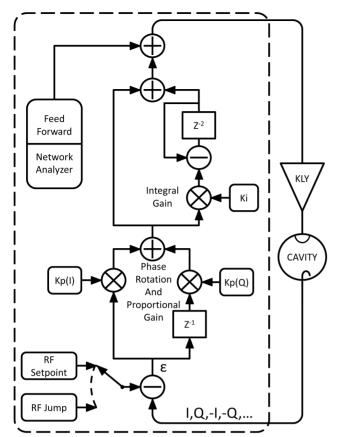

This paper explains the procedures of writing tests for control applications at the example of a low-level RF controller server for FLASH-like machines. The low-level RF system used at FLASH [2] and XFEL [3] uses ADC and DAC boards based on MicroTCA.4 [4], connected to down converters and vector modulators for 1.3 GHz controls. The machine is pulsed with 10 Hz. The control loop for the fast phase and amplitude stabilisation is running on FPGAs on the ADC/DAC boards. Trigger pulses are sent to the FPGA and with delay to the low-level RF controller server. The server is based on the DOOCS middleware and running on the frontend CPUs. It presents the interface to the control system and performs several slow tasks, like generating tables for setpoint, feed-forward, gain etc. based on input parameters provided by the operator, and executes slow control loops for drift compensation and adaptive feed-forward. This controller server is a critical element required for the operation of the machine. Therefore thorough tests are crucial to prevent machine failures and unnecessary down time.

To avert regression failures of the software staying undetected and being included in the production system during

\* martin.hierholzer@desy.de

the next software update, automated continuous integration tests should be implemented. This requires full automation of the tests.

#### VIRTUAL DEVICES

Virtual devices can be used to achieve a full automation of tests. In contrast to testing on real hardware devices, tests based on virtual devices can fully govern the function of the device. Faults can easily be injected to test exception handling.

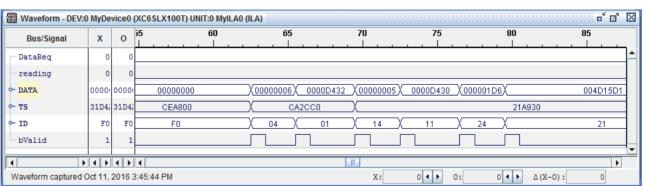

Figure 1 shows the layout of the test example. The test routines take control over the low-level RF controller server to be tested. The server is connected through a dummy register set with a state machine and a control loop algorithm reflecting the relevant behaviour of the FPGA firmware. This algorithm is connected through signal sinks and signal sources with a simple cavity model. These signal sinks and sources help creating the modularity needed for reusing parts of the virtual components for different tests.

A simple example for a test routine is shown in Figure 2. The test routine first sends the command to ramp up the gradient through the control system. Next it waits until the procedure is completed and finally it tests the result by comparing the actual current gradient of the cavity model with the nominal set point.

The virtual devices used for the test may be an imperfect approximation of the real devices. This presents no issue if the approximation is good enough for the application to function normally. In this particular case the actual control loop is not part of the test, which strongly relaxes the requirements on the cavity model. The control loop implementation and the cavity model can be tuned to each other to minimise the effort. Faults (like quenches of super-conducting cavities) don't need to be properly simulated, as long as there is no sensitivity in the tested software to those details. Simply switching off the measured signal might be enough to simulate such condition.

# USE VIRTUAL TIME TO AVOID RACE CONDITIONS

The example test routine shown in Figure 2 uses a system time-based sleep function to wait until the ramup procedure is completed. This approach severly suffers from potential race conditions: A fault shall be injected at a particular point of the rampup procedure. The test routine is running asynchronously to the server in a separate thread. To inject the fault in the right moment, the sleep time between starting the rampup procedure and the fault injection has to be tuned precisely. Otherwise, the fault may be injected in a different

Figure 1: The layout of the test of the low-level RF controller server based on VirtualLab. The box at the bottom represents the low-level RF controller server to be tested.

```

// tell the server to ramp up the RF

doocsSet("//AUTOMATION/START_RAMPUP", 1);

// wait until shortly before some safety check

sleep( (numberOfRfPulsesUntilCheck-1)*100ms + someExtraTime );

// inject a fault

cavityModel.injectFault();

// wait one RF pulse to perform the check

sleep(100ms);

// check if drive signal was switched off

BOOST_CHECK( cavityModel.driveSignal == 0.0 );

```

Figure 2: Pseudo-code of a simple test routine, which is not based on virtual time and thus subject to race conditions.

RF pulse than intended, which might trigger some other, unexpected error handling. If the system is busy with other tasks, the wakeup might be delayed, or the server might take slightly longer than usual and the wakeup might relativly be early. Spurious false failues of the tests might occur as well as occasioally passing the test successfully despite of bugs in the code.

To eliminate these race conditions, the threads need to be synchronised properly. This can be done by introducing the concept of virtual time. Figure 3 shows a test routine, where the system time-based sleep has been replaced with a command controlling the virtual time. This command will instruct the virtual timer shown in Figure 1 to send as many timer events as necessary to move forward by the requested amount of virtual time. This will trigger the generation of data by the model. Also the appropriate number of RF pulse

```

// tell the server to ramp up the RF

doocsSet("//AUTOMATION/START_RAMPUP", 1);

// synchronously wait until before the safety check

virtualTimer.advanceTime(numberOfRfPulsesUntilCheck*100ms);

// inject a fault

cavityModel.injectFault();

// synchronously wait for one RF pulse

virtualTimer.advanceTime(100ms);

// check if drive signal was switched off

BOOST_CHECK( cavityModel.driveSignal == 0.0 );

```

Figure 3: Pseudo-code of a simple test routine based on virtual time to avoid race conditions.

interrupts will be sent to the control server to trigger its processing.

To make sure no race conditions can take place, it also has to be made sure that the server has finished processing before the command returns. The exact implementation for this may depend on the control system middleware and/or the application.

# ACCOUNT FOR SLOW MODEL COMPUTATIONS

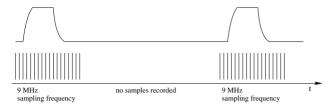

A typical signal sampling frequency for the RF control application is around 9 MHz. Today's CPUs are not capable of computing the simple cavity model at this frequency by far, especially if multi-cavity setups have to be taken into account. As shown in Figure 4, there are no samples recorded during the gap between the RF pulses. Typical pulse lengths are in

pyright © 2017 CC-BY-3.0 and by the respective

Figure 4: Typical signal sampling for pulsed mode operation. The ratio of pulse lengthes and gap time between the pulses is not to scale.

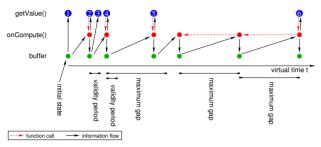

Figure 5: Sketch of the signal sources' efficient handling of request for new values. The blue circles on the top represent the requests via a call to getValue() incoming in the sequence of the numbers inside each circle. The red circles in the middle represent the calls to the callback function onCompute() which triggers computing a new model state. The green circles at the bottom represent the entries in the buffer storing the computed states for later re-use. New states are computed according to the configured validity period and maximum gap time. Request 3 does not require a computation, since it falls within the validity period of the previously computed value. Request 6 exceeds the maximum gap time, which triggers the computation of additional intermediate states.

the order of around 2 ms at a repetition rate of  $10 \, \text{Hz}$ , thus  $98 \, \%$  of the computations can be saved.

Even a preliminary continuous wave setup of the low-level RF controls used for the ELBE accelerator [5] uses this sampling scheme in the interface between firmware and software, while the control loop is constantly running also in between the "pseudo pulses". Since the performance of the RF control in the virtual test setup is unimportant for the software tests, the sampling frequency of the control loop can be strongly reduced in between the pseudo pulses. In more complex test setups, other model computations may be required at a totally different rate or potentially even only triggered by some kind of event.

To achieve the required flexibility for this and similar use cases, VirtualLab will not sample all components with the same, constant sampling frequency. Instead, a component will request a sample from its connected components as needed. This mechanism is built into the signal sinks and sources shown in Figure 1. The arrows between the sinks, sources and calculation blocks represent requests for new values. Since control loops and models often depend on the

history, each signal source must be able to return a value for any given time stamp within certain limits.

Each signal source has a smart, internal buffer to efficiently handle the incoming requests with minimal effort. Figure 5 shows how a signal source handles incoming requests. The signal source has a number of tuning parameters which allow to reduce the number of samples which need to be computed. Most important are the validity period, within which an already computed sample can just be reused, and the maximum gap time which governs the insertion of additional intermediate computations needed to keep the model precision within acceptable limits. The maximum gap time is especially important for the continuous wave setup, which makes sure that the model is computed also between the pseudo pulses with reduced sampling rate.

#### CONCLUSION AND OUTLOOK

The VirtualLab framework has been used successfully to develop tests for the low-level RF controller server for the ELBE accelerator at HZDR. All hardware has been replaced by virtual implementations, so the tests can be run on a standard PC. Its execution is triggered by commits to the source code management system or completed tests of dependencies used by the controller server. This presents a full continuous integration test chain.

By introducing virtual time, the problem of race conditions between the test routine and the tested software has been eliminated. To achieve an execution speed close to a real setup with actual hardware, model samples are computed only when needed. This mechanism is implemented in the signal sinks and sources which connect the different components of the virtual setup.

To further reduce the CPU load, an interpolation between the samples will be implemented in future. In additon, more complex test environments will be made possible by allowing to share virtual devices and model components across server executables and thus testing the interplay of multiple control servers.

#### **REFERENCES**

- [1] ChimeraTK, http://github.com/ChimeraTK

- [2] C. Schmidt *et al.*, "Real time control of RF fields using a MicroTCA.4 based LLRF system at FLASH", 19th IEEE Real-Time Conference, Nara, Japan, 2014.

- [3] M. Altarelli *et al.*, "XFEL: The European X-Ray Free-Electron Laser: Technical Design Report", *DESY-2006-097*, DESY, Hamburg, 2007.

- [4] PICMG<sup>®</sup>, "MicroTCA<sup>®</sup> Enhancements for Rear I/O and Precision Timing, MicroTCA.4 R1.0", 2011/2012.

- [5] M. Kuntzsch et al., "First experience using a MicroTCA.4-based LLRF-controller driving the SSPA-based high power RF system at ELBE", Ninth CW and High Average Power RF Workshop, Grenoble, France, 2016.

#### DEVELOPMENT AND CURRENT STATUS OF A CARBORNE GAMMA-RAY SURVEY SYSTEM, KURAMA-II

M. Tanigaki\*, R. Okumura, K. Takamiya, N. Sato, H. Yoshino, H. Yoshinaga, Y. Kobayashi Research Reactor Institute, Kyoto University, Kumatori, Osaka 590-0494, Japan

Abstract

A carborne gamma-ray survey system, named KURAMA (Kyoto University RAdiation MApping system), was developed as a response to the nuclear accident at TEPCO Fukushima Daiichi Nuclear Power Plant in 2011. A CompactRIO-based system KURAMA-II has been developed as the successor of KURAMA, and served for various activities on the radiation monitoring in Eastern Japan. We continue developing KURAMA-II as a tool not only for the current monitoring activities, but also for the immediate responses in nuclear incidents in future. The current status and on-going developments of KURAMA-II will be introduced along with the recent status of the east Japan.

#### INTRODUCTION

The magnitude-9 earthquake in Eastern Japan and the following massive tsunami caused a serious nuclear disaster of Fukushima Daiichi nuclear power plant. Serious contamination was caused by radioactive isotopes in Fukushima and surrounding prefectures. KURAMA [1] was developed to overcome the difficulties in radiation surveys and to establish air dose-rate maps during and after the present incident. KU-RAMA enabled operations of a large number of in-vehicle units for large-scale surveys owing to its high flexibility in the configuration of data-processing hubs or monitoring cars. KURAMA has been successfully applied to various activities in the radiation measurements and the compilation of radiation maps in Fukushima and surrounding areas.

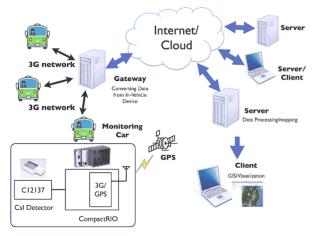

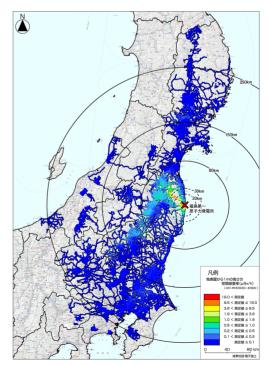

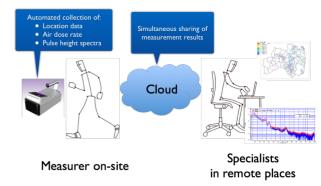

Figure 1: System outline of KURAMA-II.

As the situation becomes stabilized, the main interest in measurements moves to the tracking of the radioactive materials that have already been released into the environment surrounding the residential areas. Such monitorings can be realized efficiently if vehicles that periodically move around the residential areas, such as local buses, delivery vans or postal motorcycles, have compact and full-automated KU-RAMAs onboard. KURAMA-II [2] is designed for such purposes, characterized by its compactness, autonomous operation, and additional functions such as the measurement of pulse height spectrum. In this paper, the system outline of KURAMA-II as well as the results of continuous monitoring using KURAMA-II will be introduced.

#### SYSTEM OUTLINE OF KURAMA-II

Long term (in the order of tens of years) and detailed surveillances of radiation are required in the residential areas exposed to the radioactive materials by the nuclear accident. Such monitoring can be realized by implementing radiation monitoring units into moving vehicles in residential areas such as local buses, delivery vans or postal motorcycles. KURAMA-II is developed for such usages.

System outline of KURAMA-II is shown in Fig. 1. KURAMA-II stands on the architecture of KURAMA, but the in-vehicle part is totally re-designed for the autonomous, continuous operations in vehicles [3]. The platform is replaced from a conventional laptop PC to a CompactRIO controller of National Instruments to obtain better toughness, stability and compactness. The radiation detection part is replaced from the conventional NaI survey meter to a Hamamatsu C12137 [4], a CsI detector characterized as its compactness, high efficiency, direct ADC output and USB bus power operation. The mobile network and GPS functions are handled by a Gxxx module for CompactRIO by

Figure 2: In-vehicle unit of KURAMA-II. A CsI detector and a CompactRIO controller are compactly placed in a tool box with the size of 34.5 cm  $\times$ 17.5 cm  $\times$ 19.5 cm.

CC-BY-3.0 and by the respective authors

<sup>\*</sup> e-mail:tanigaki@rri.kyoto-u.ac.jp

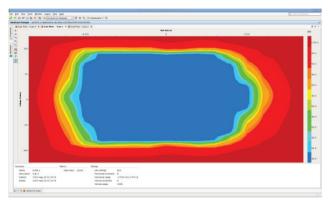

Figure 3: The result of continuous monitoring by local buses etc. in Fukushima as of the fourth week of September 2016. This kind of maps are released both in picture and in data files (csv and kmz) through the web on weekly-basis.

SEA. All components of the in-vehicle unit are placed in a small tool box for the better handling (Fig. 2).

The software for KURAMA-II is basically the same code as that of original KURAMA, with additional developments for newly introduced C12137 detector and Gxxx module, for the start up and initialize sequences fautonomous operation, and for a RESTful-based file transfer protocol.

All the data collected by in-vehicle units are shared over Dropbox, a cloud storage service. The gateway server is prepared as the interface between in-vehicle units and Dropbox because it does not currently support CompactRIO. A feasibility study of ownCloud with the implementation of data transfer protocol of KURAMA-II is on the way as the alternative cloud storage for KURAMA-II system, not only to eliminate the gateway server, but also to obtain more flexibility in the cooperative operations with other databases, such as GIS servers.

#### OPERATIONS OF KURAMA-II IN EASTERN JAPAN

#### Continuous Monitoring by Local Buses

One of the major application of KURAMA-II is the continuous monitoring in residential areas by local buses. A series of field tests on local buses started in December 2011 have finally evolved into the official project organized by Fukushima prefectural government under the collaboration of Kyoto University and JAEA [5]. As of October 2016, more than fifty KURAMA-II units are continuously operated throughout Fukushima prefecture. In-vehicle units are deployed not only to local buses, but also to official vehicles operated by Fukushima prefectural government for purposes other than radiation monitoring. In the case of local buses, the bus routes in each operation areas are completed over three to five days typically, based on the transportation plan determined by its respective bus operator. The air dose rate at 1 m above on the road is determined by multiplying the shielding factor of bus body determined by the comparison with the results of periodical carborne surveys by Japanese

Figure 4: Typical example of the decontamination effect observed through monitoring by KURAMA-II on a local bus. In this figure, a drastic reduction of air dose rate along with the decontamination was observed.

government. The results from this project is released to the public from the web site on a weekly basis (Fig. 3). The changes of radiations in residential areas are successfully observed (Fig. 4).

#### Periodical Surveys by Japanese Government

The Nuclear Regulation Authority (NSR) in Japan conducts the periodic carborne surveys in Eastern Japan since 2011 [6, 7]. This project has been taken over to Nuclear Regulation Authority (NSR) because of the reorganization of atomic energy administration in Japan. In this project,

Figure 5: A typical map of air dose rates on roads measured by KURAMA-II from June to August in 2014 [7].

ISBN 978-3-95450-189-2

14

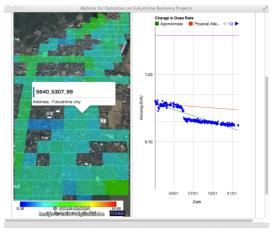

around one hundred KURAMA-II are deployed to the local municipalities in Eastern Japan twice a year, and the staff members in each municipality drive around their own municipalities with in-vehicle units (see Fig. 5). The summarized data is released through the websites [8,9] as well as served for various analyses including the evaluation of ecological half-lives of radioactive cesium in environment and the long-term predictions of air dose rates in Fukushima [10] (Fig. 6).

Figure 6: Prediction of air dose rate in the area within 80 km from the Fukushima Daiichi Nuclear Power Plant [10]. The parameters used for these predictions are determined by using the data of carborne surveys by KURAMA-II.

#### ON-GOING DEVELOPMENT

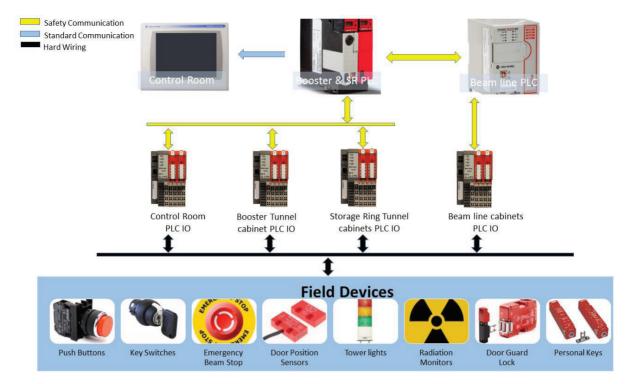

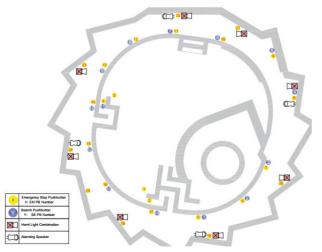

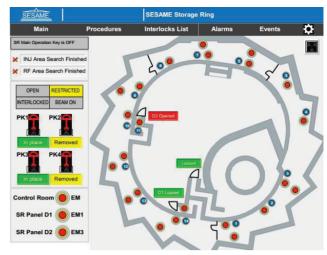

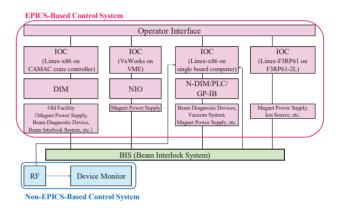

One important lesson we learned from the experience in the Fukushima accident is that the quality of data in a monitoring activity under emergency situation can be easily and severely suffered by human errors. For example, almost half of data was suffered by human errors in one of the large-scale monitoring activities performed by several hundreds of scientists, who were considered to be the specialists on this kind of activities. Efforts and costs to recover such errors sometimes become sufficient to terminate the activity itself.