# Demonstration of an ATCA based LLRF Control System at FLASH

Stefan Simrock, DESY for the XFEL LLRF team

#### Outline

- Introduction: xTCA for Physics

- RF Control for the European XFEL

- ATCA based RF Control System

- Demonstration at FLASH

## xTCA for Physics

#### **ATCA Standard**

Advanced Wezzanine Card

From Computer Desktop Encyclopedia Reproduced with permission. @ 2006 Schroff Bectronic Solutions

#### xTCA for Physics

- Adapt xTCA for physics use by:

- Extensions to specifications

- Guidelines

- Open source solutions

- Building on existing xTCA base under PICMG rules

- Approval by PICMG membership vote

- Collaborate with industry for vendor support

http://www.picmg.org/pdf/PICMG\_Physics\_Public\_Web\_Update\_ 061209\_R5-3.pdf

See also: THA006 New Hardware and Software

Developments for the XFEL (K. Rehlich)

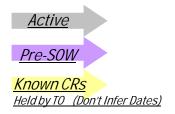

#### Excerpt from Time Line for xTCA Specs.

*IRTM* ATCA 3.0 CR Exists

3.1 R2

High Speed Ethernet

AdvancedTCA Extensions

uTCA.O CR Exists

uTCA.3

Conduction Cooled

xTCA Physics

Physics xTCA I/O, Timing &

Synchronization

Physics xTCA Software Architectures & Protocols

2009

2010

#### Industrial LLRF in xTCA Standard

## ATCA Design for LLRF

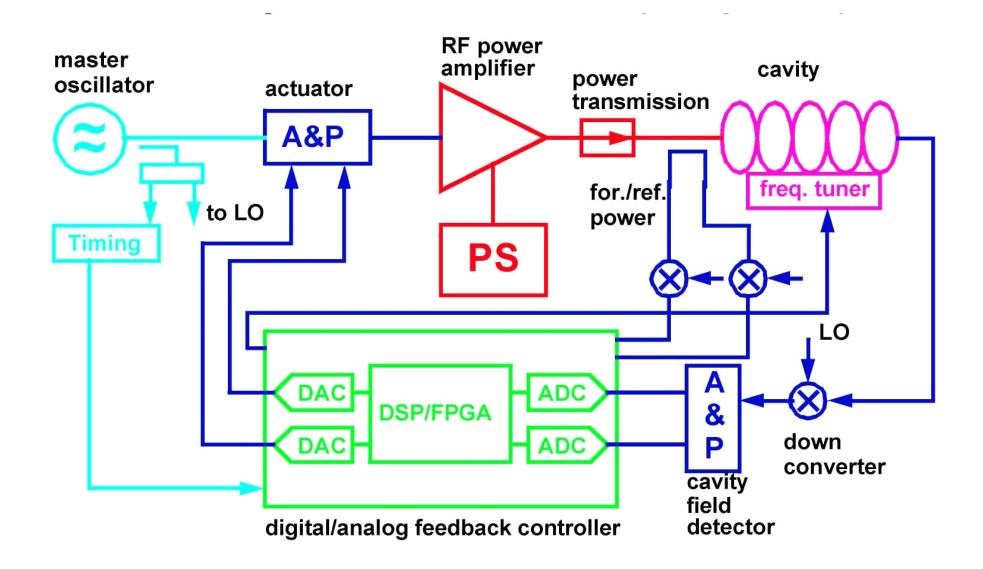

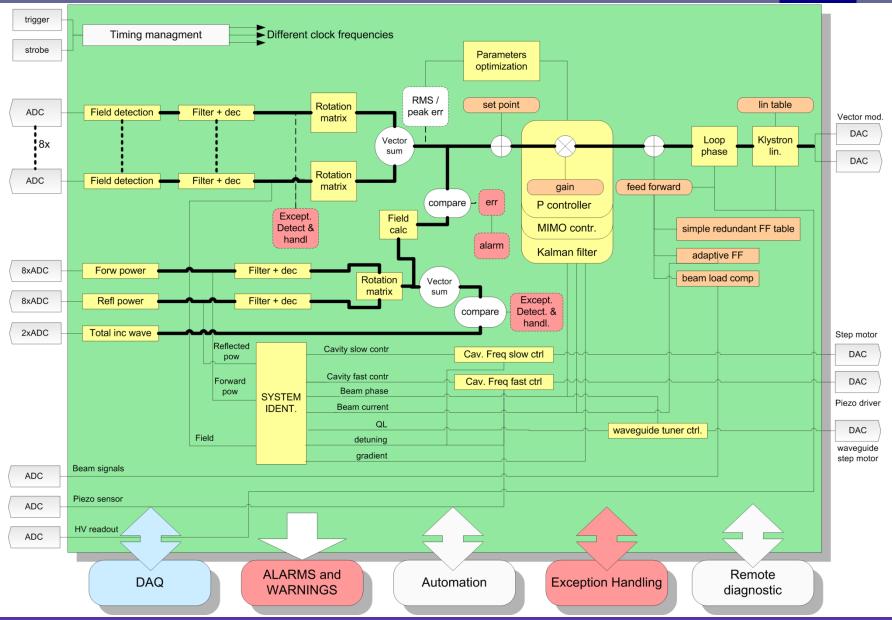

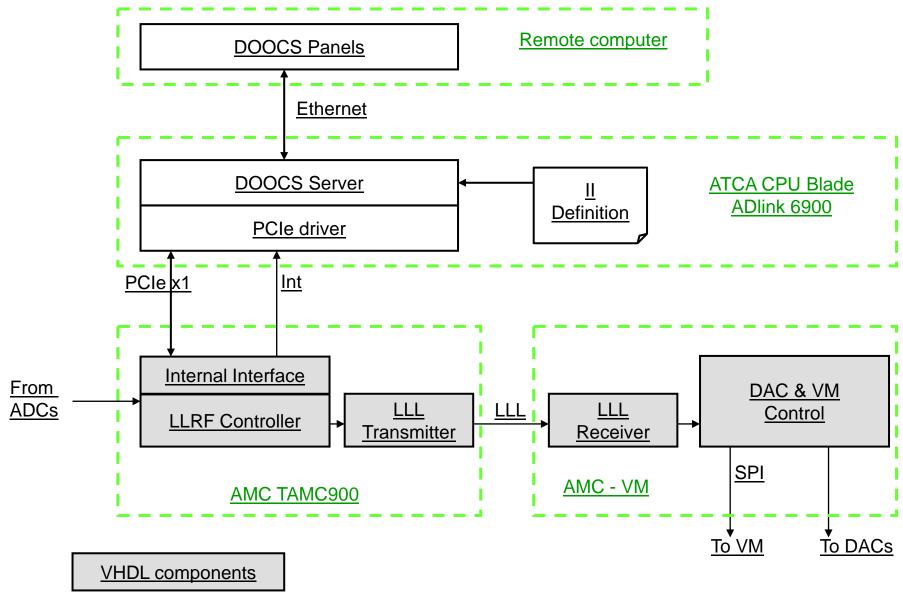

#### Architecture of LLRF System

#### Decision for ATCA

- Future RF Control systems will require simultaneous data acquisition of up to 100 fast ADC channels at sampling rates of around 100 MHz and real time signal processing within a few hundred nanoseconds.

- At the same time the standardization of low-level systems are common objectives for all laboratories for high availability, high performance, and moderate cost.

- Also desirable are modularity and scalability of the design as well as compatibility with accelerator instrumentation needs including the control system.

- All these requirements can be fulfilled with the new telecommunication standard ATCA

#### Architecture of LLRF System

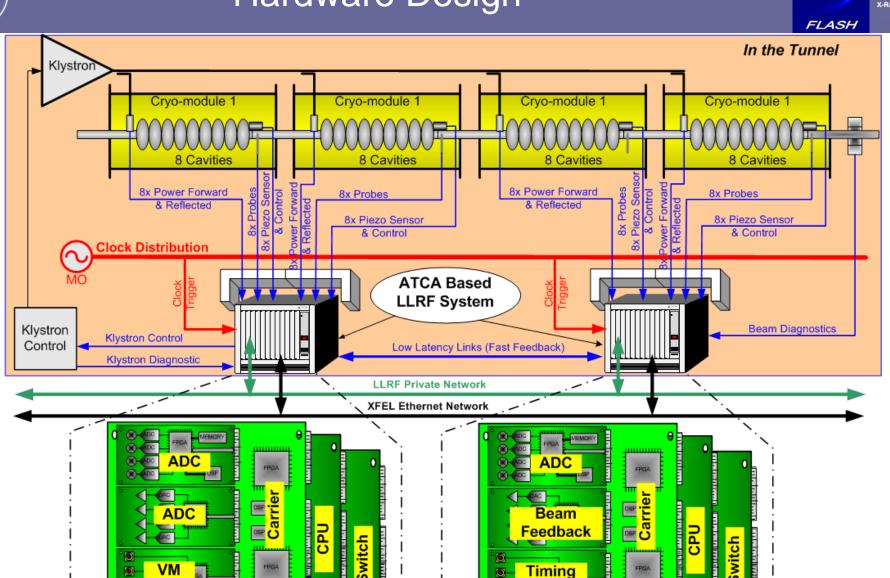

#### Hardware Design

POWER SECTION

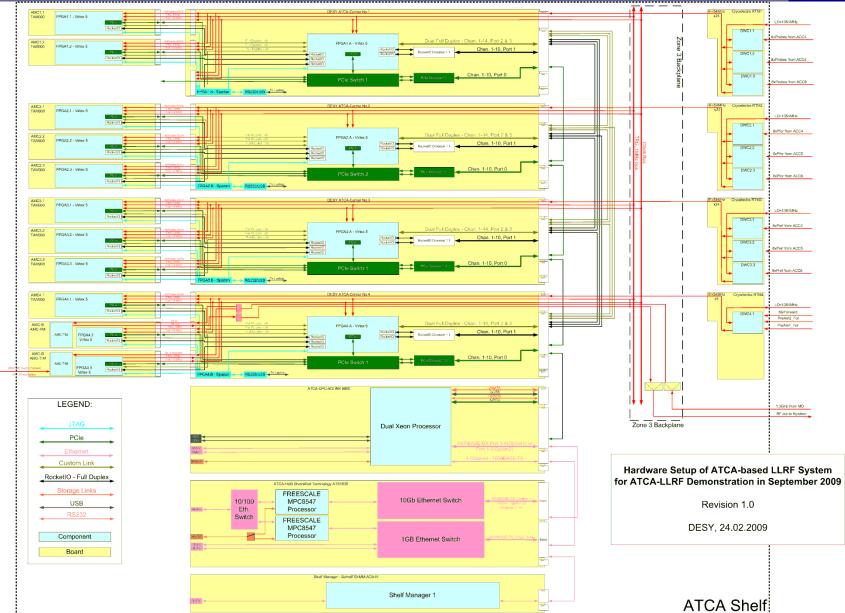

#### Configuration of LLRF in ATCA Crate

#### Software Design

#### Application, Resources and Commlinks

FLASH

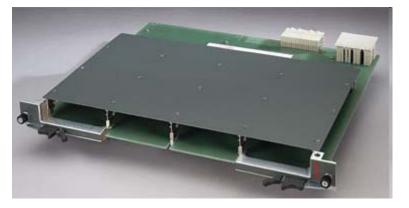

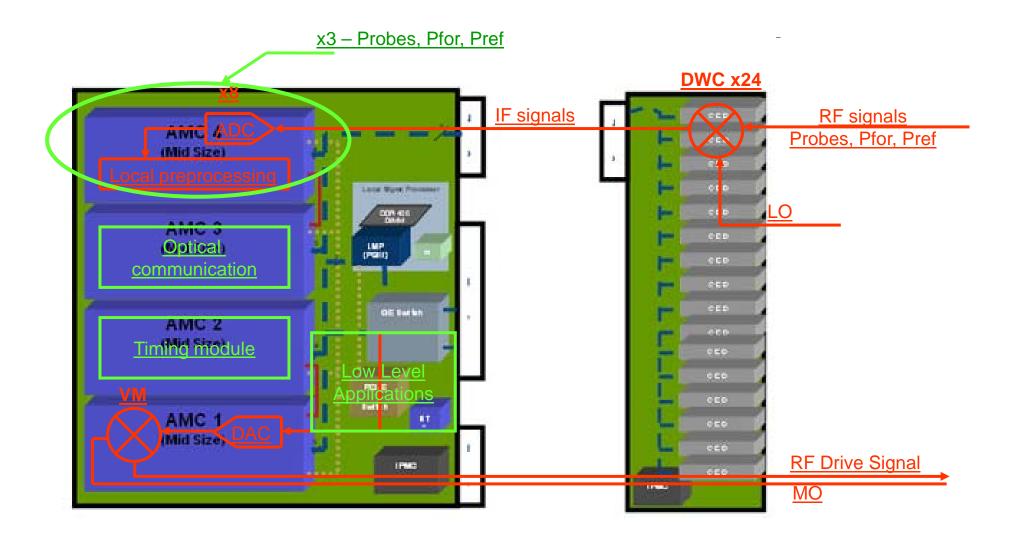

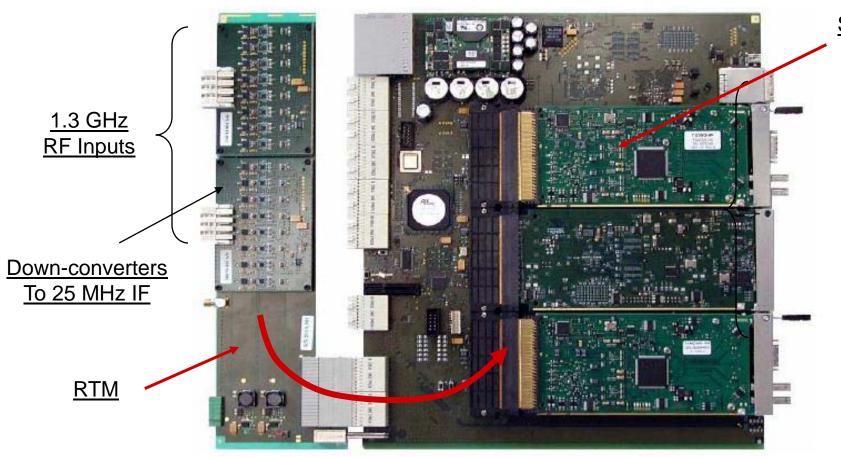

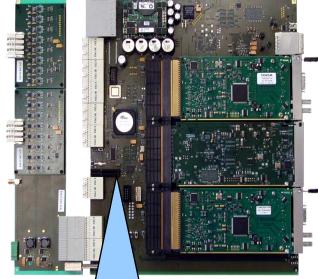

#### ATCA Carrier with AMC slots and RTM

#### ATCA-based LLRF control system

Stacked 1-wide

AMC ADC's &

IO AMC's,

connectors

105 MHz 14 bit 8 Ch COTS ADC's

### ATCA Demonstration at FLASH

#### **Demonstration Goals**

| Objective                            | Comment                                                                                                                      |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Analog IO                            | Demonstrate the noise added from entrance to rear transition module through Zone 3 and carrier to AMC module is not degraded |  |  |  |

| Communication links                  | Demonstrate that the scheme of Low Latency Links, PCIe and GbE is functional.                                                |  |  |  |

| Operation in accelerator environment | Demonstrate that the ATCA based LLRF is functional in the noisy accelerator environment.                                     |  |  |  |

| Rear transition module               | Demonstrate the concept of rear transition modules with downconverters                                                       |  |  |  |

| Timing distribution                  | Demonstrate timing distribution functionality                                                                                |  |  |  |

| Timing jitter                        | Demonstrate that the measured timing jitter is adequate for LLRF control.                                                    |  |  |  |

| IPMI                                 | Demonstrate the IPMI implementation.                                                                                         |  |  |  |

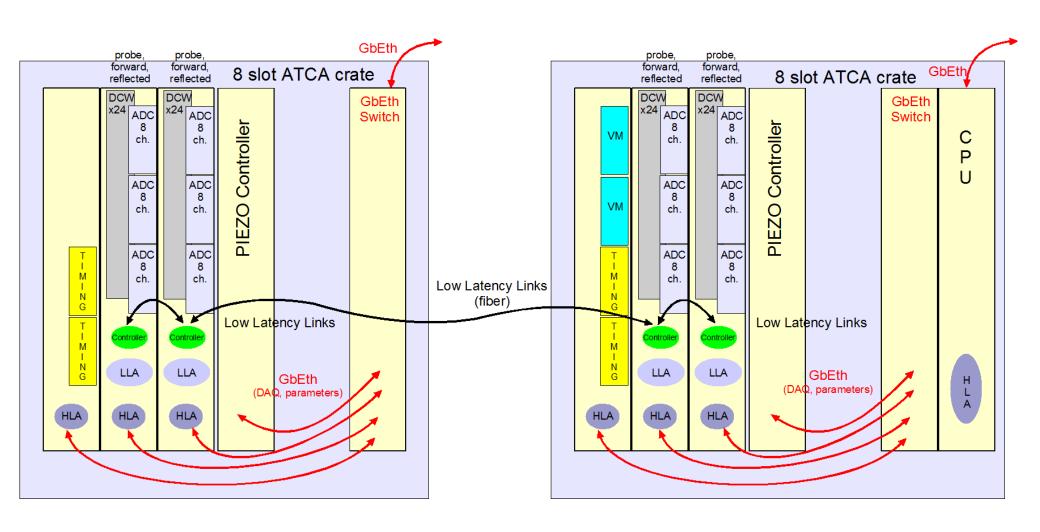

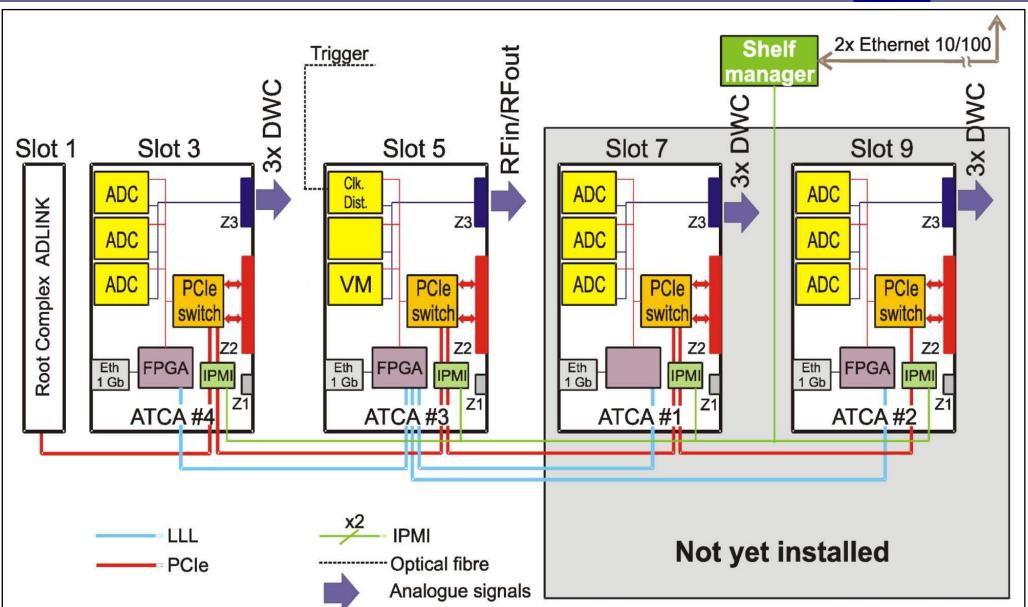

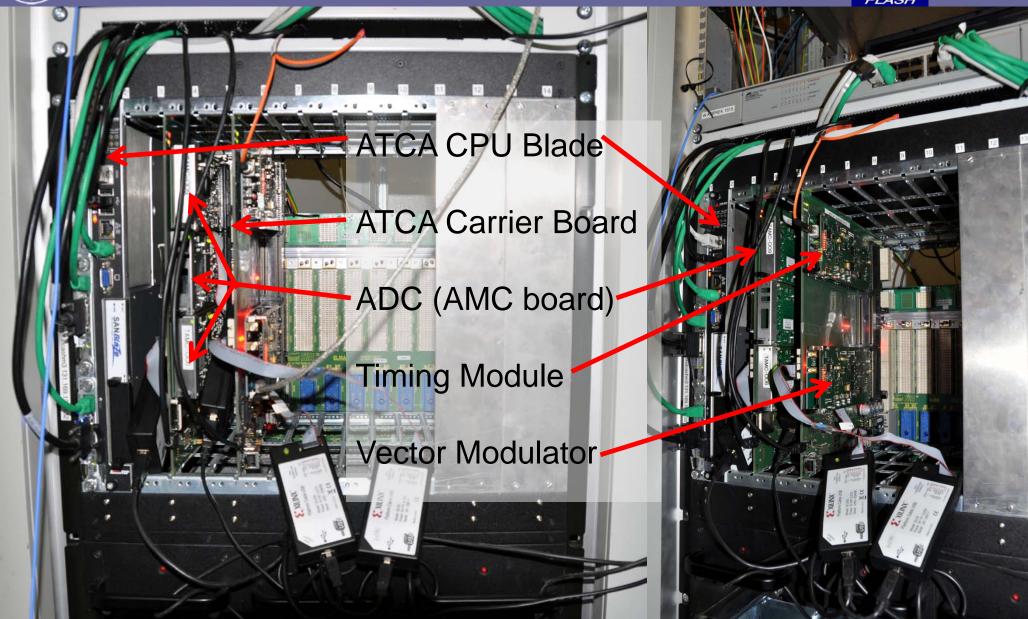

#### ATCA Configuration at FLASH

#### Software Architecture

#### Intelligent Platform Management (IPMI)

- Management of ATCA carrier board,

- Management of AMC modules,

- Monitoring of ATCA health (diagnostics),

- E-Keying for PCIe, Gb Ethernet and user defined Low Latency Connection,

- Monitoring of temperature, power supply, clocks, etc...

IPMC

ATMEGA 1281

microcontroller with

dedicated

management hardware

#### Set-up at FLASH with 2 carrier boards

#### Set-up in Lab with 4 Carrier Boards

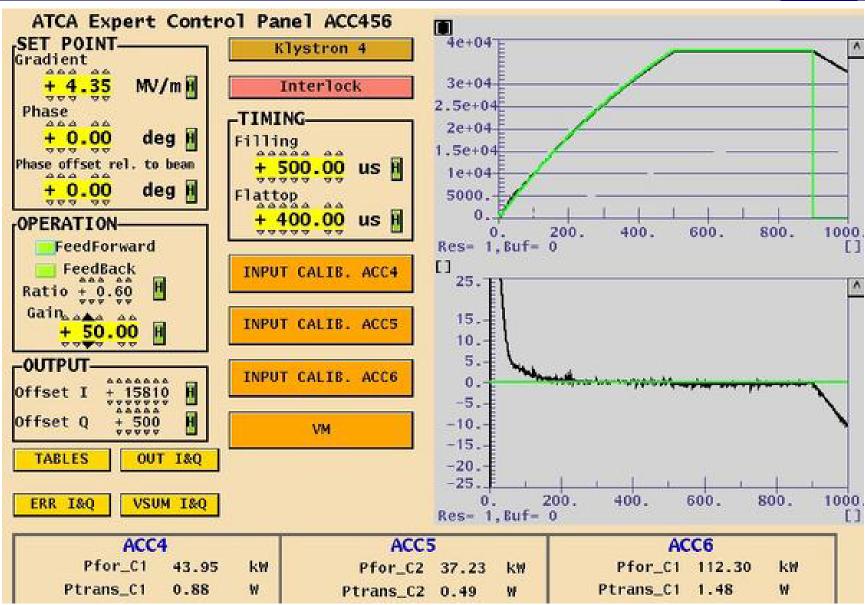

#### Operator Interface

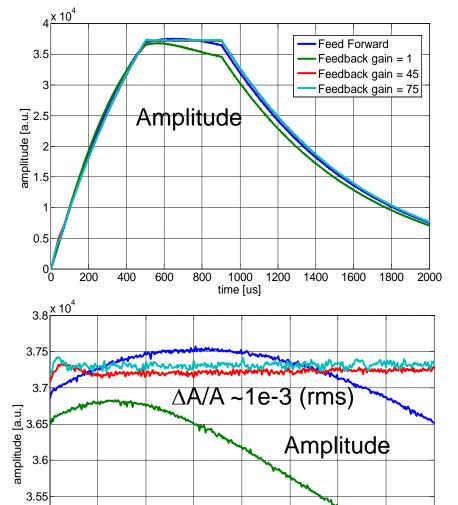

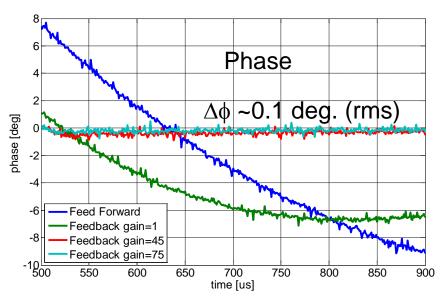

#### Amplitude and Phase Control

Feed Forward

550

3.45 500 Feedback gain = 1

Feedback gain = 45

Feedback gain = 75

600

650

700

time [us]

750

800

850

900

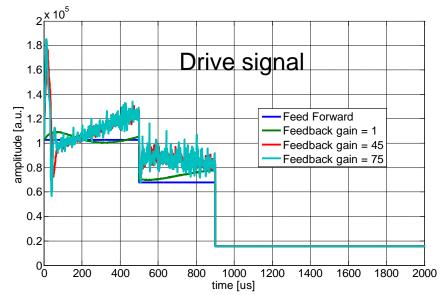

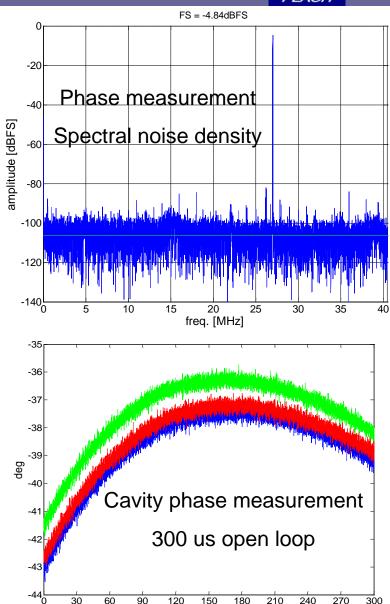

#### Crosstalk, Noise and Timing Jitter

#### **Preliminary Performance Data**

- Channel isolation >80 dB @50MHz (presently limited by downconverter)

- Noise < 200 μV (rms) consistent with 14-bit ADC, 200 MHz bandwidth

- Timing jitter < 15 ps (rms) @ 81 MHz (upper limit, could be dominated by RF

|         | ADC1   | ADC2   | ADC3   | ADC4   | ADC5   | ADC6   | ADC7   | ADC8   |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| ADC1 on | -67.87 | -48.14 | -66.86 | -66.39 | -73.71 | -69.90 | -67.11 | -71.38 |

| ADC2 on | -48.35 | -67.79 | -68.14 | -74.08 | -69.35 | -71.00 | -67.86 | -72.67 |

| ADC3 on | -59.51 | -66.47 | -68.09 | -52.43 | -66.08 | -70.39 | -66.98 | -72.60 |

| ADC4 on | -65.52 | -69.55 | -49.03 | -68.03 | -68.82 | -69.81 | -66.69 | -70.78 |

| ADC5 on | -73.27 | -73.27 | -67.81 | -69.82 | -66.44 | -44.35 | -63.30 | -69.77 |

| ADC6 on | -2.92  | -0.45  | 0.56   | -3.24  | 17.30  | -8.12  | 4.08   | 8.28   |

| ADC7 on | -76.22 | -70.18 | -69.39 | -77.31 | -65.34 | -70.27 | -68.47 | -45.76 |

| ADC8 on | -70.80 | -63.62 | -62.15 | -69.65 | -67.48 | -62.79 | -52.15 | -64.50 |

time[us]

#### Conclusion

- The demonstration of an xTCA based LLRF system at the FLASH user facility has verified that this standard can be employed for a wide range of physics applications:

- ATCA for large scale and high performance systems

- μTCA for low cost instrumentation needs

- and combinations of these standards

- Although standard is quite new commercial components and even complete systems are already available for physics applications.

- Several physics labs are already using or evaluating the ATCA and μTCA standard

- xTCA for physics standardization effort between labs and industry will release first specifications in 2010 and should lead to commercially available products within 1-2 years.